前言

本文主要为初学和首次使用ModelSim软件的学习者所提供,对已经学习和掌握ModelSim软件的帮助不大,本篇文章不对代码报错等相关代码的若干问题进行解决与提供方法,有问题可以邮件进行交流。

基本使用

第一:工程的创建

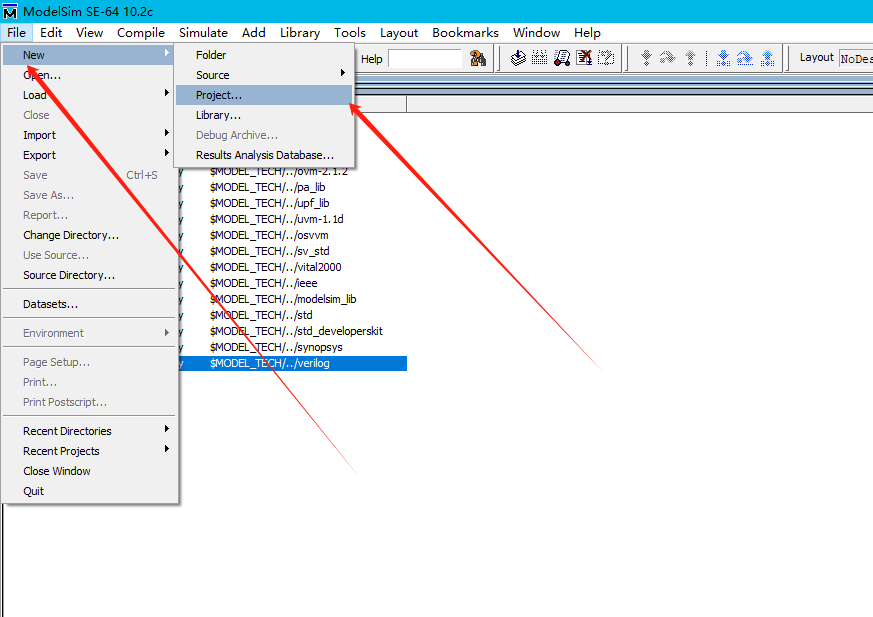

打开ModelSim软件,左上角选择File-New-Project。

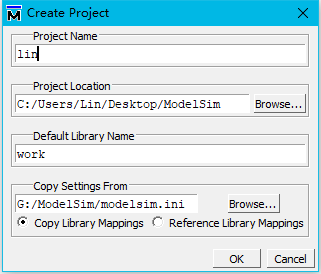

第一栏为文件名称,根据要求进行命名,第二栏为文件路径,根据自己需要选择位置,不要选择中文路径,以免出现未知错误。其余信息默认就可以,不需要进行更改,随后点击OK即可。

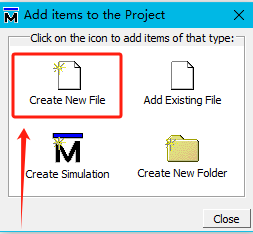

成功后会弹出一个创建文件的提示窗,选用Create New File。

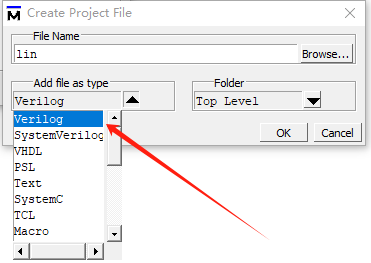

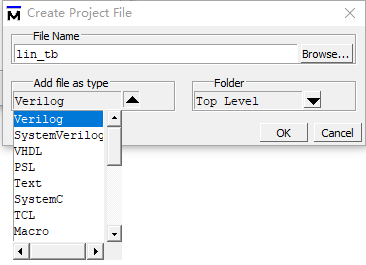

我们需要创建两个文件,一个文件为源程序,一个文件为测试程序。源程序的程序名按自己需求填写,值得注意的是,箭头指明的文件类型一定要是Verilog类型,默认的是VHDL类型,务必进行自行勾选,随后点击OK即可。

创建测试文件时,命名可以为源程序名后加TB,也就是Test Bench,箭头指明的文件类型一定要是Verilog类型,默认的是VHDL类型,务必进行自行勾选,随后点击OK即可。

至此工程就创建完毕了,双击相应文件就可以进行编写代码的操作。

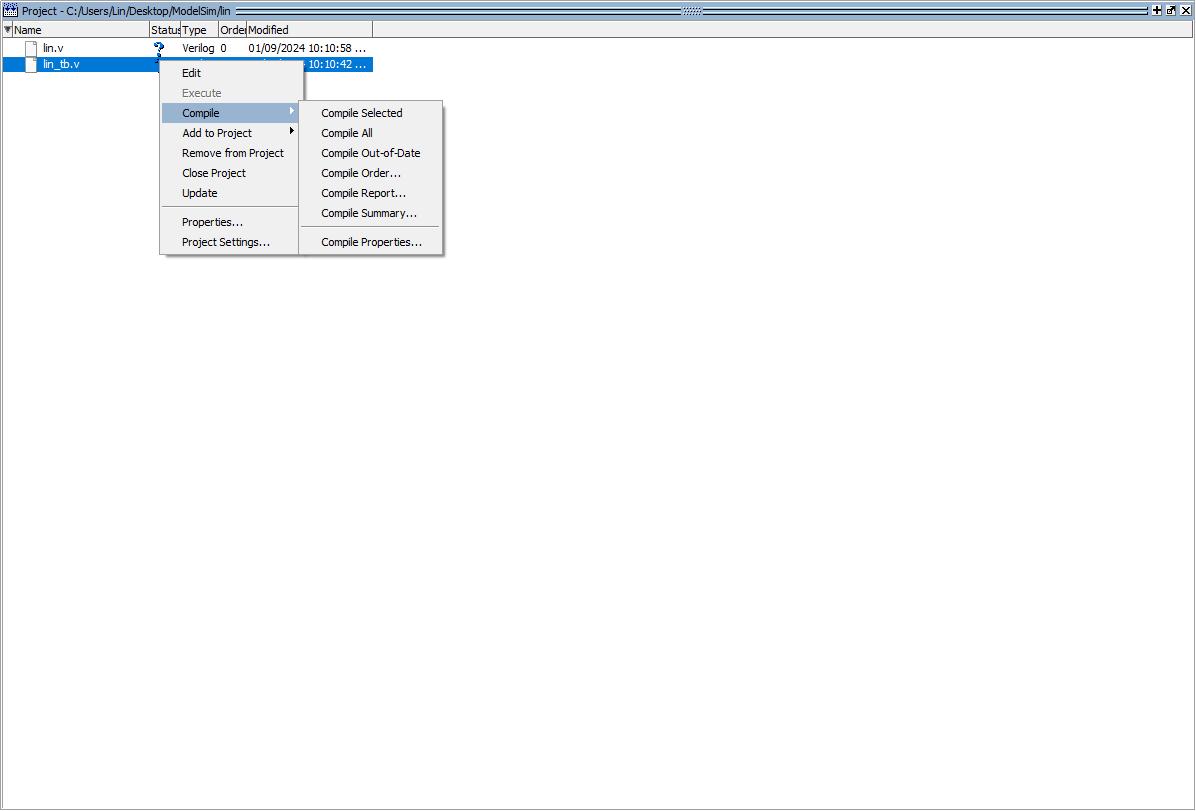

第二:工程的基础编译

未经过编译或者被修改过的文件会提示一个问号,进行编译Compile Selected操作过后会提示一个绿色的勾,证明你的程序没有问题,如果出现报错请查看报错原因进行修改。

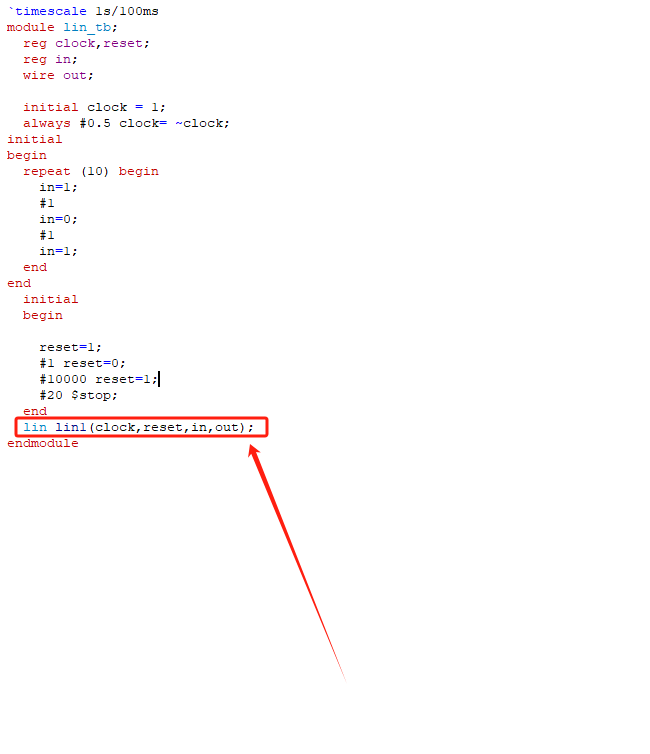

测试程序其他部分在学习中已经很明确,提到比较少的模块例化我再次提起一下,模块例化前面是我们源程序的模块名,后面跟的例化出来的文件名可以任意。

编译这部分基本上没有太多的内容,主要是对报错的修改。

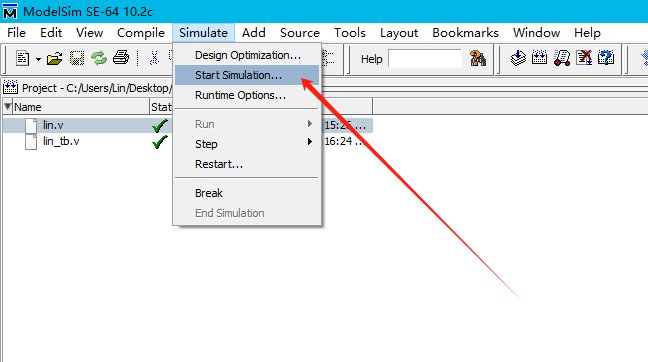

第三:工程的基础仿真

首先保证编译已经全部通过,最后选择头部菜单栏的Simulate,然后选择Start Simulate。

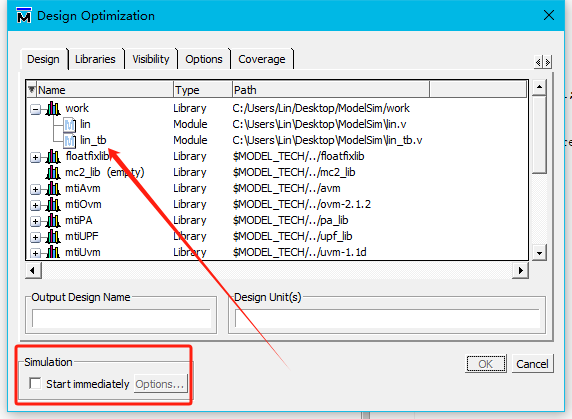

到这里我们选择我们的工作文件Work,选中我们的测试程序,切记方框内默认是打勾的,记得把勾去掉,暂时用不上。

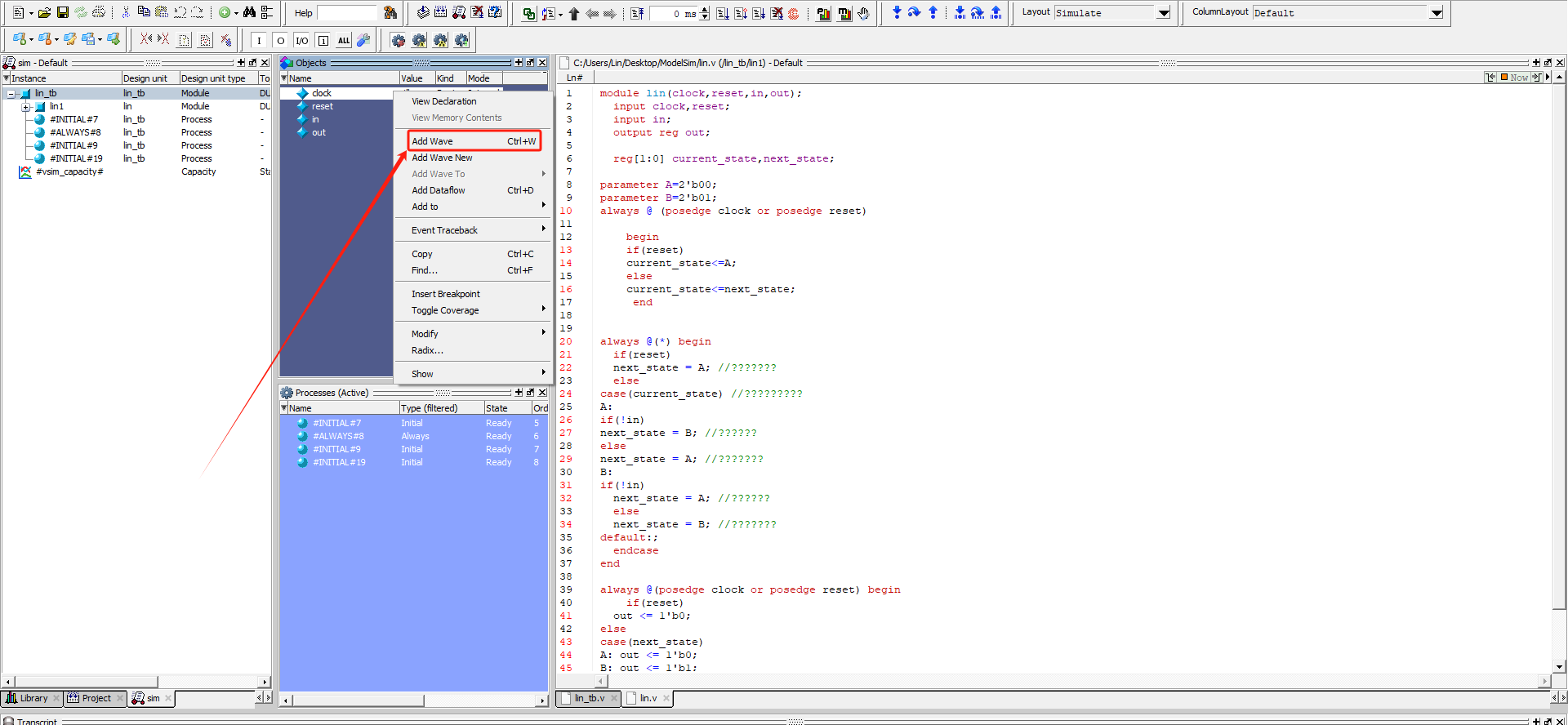

进入仿真页面后,右击对应信号,将所需信号添加至仿真观察图当中。

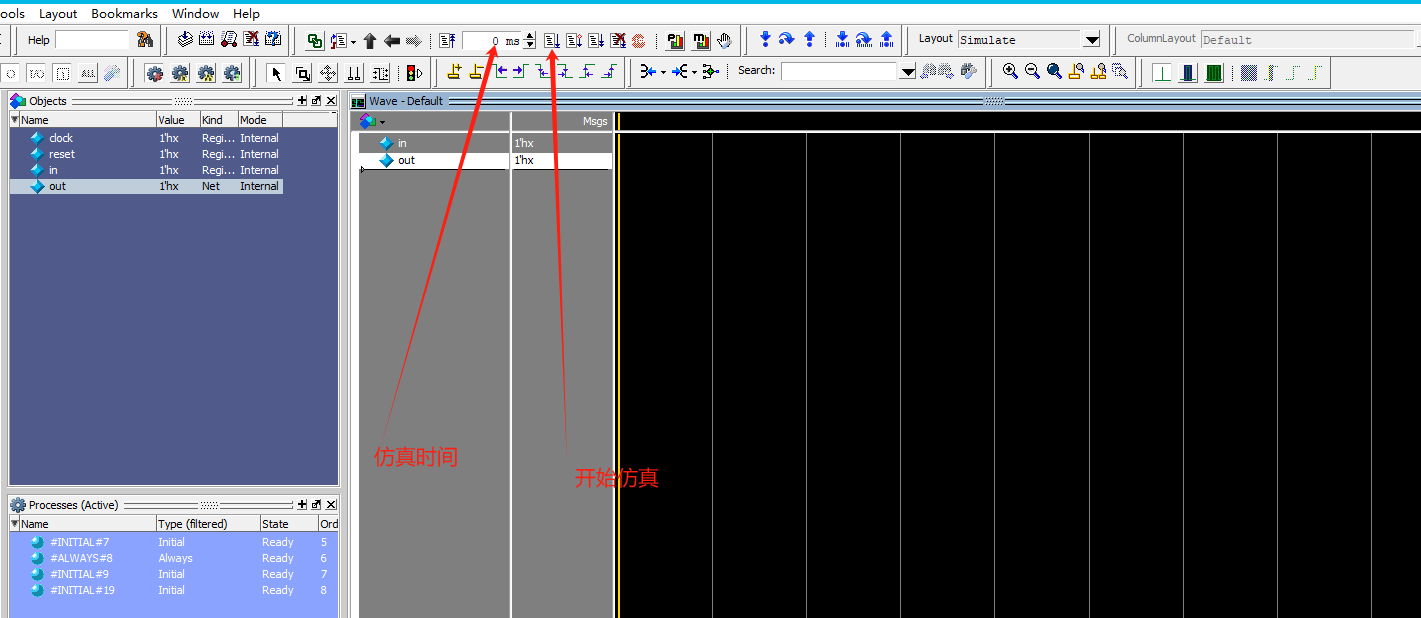

注意仿真时间和仿真开始按钮,设置好仿真时间后,仿真会按既定的时间进行运行,如果发现图像没有任何变化,查看仿真时间是否过短或者测试代码时间精度是否存在问题,最后考虑是否为程序逻辑问题。

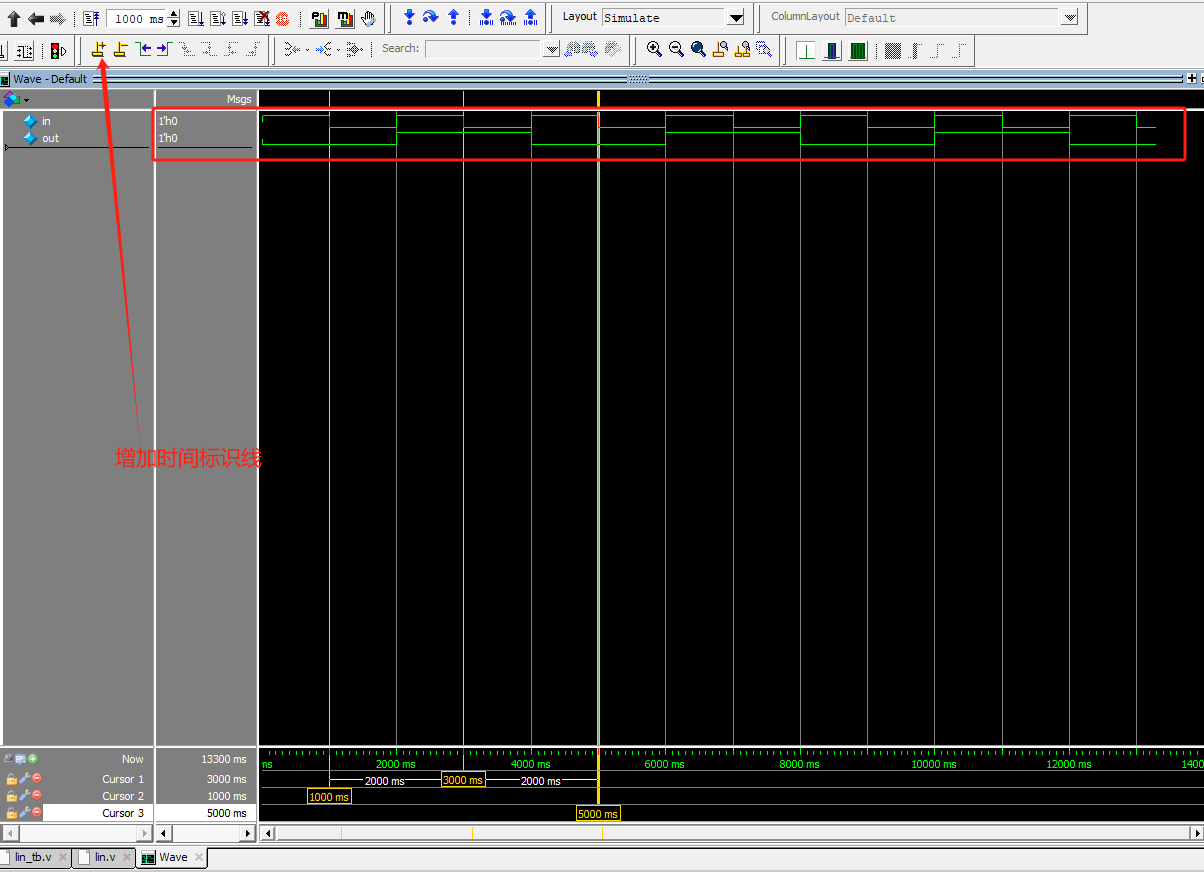

程序主要逻辑在于方框内内容的判断,需要根据实际代码情况查看,因为只做仿真的基础演示,这里不作示例。

后记

此教程只对ModelSim作了简单的使用讲解,为入门级别讲解,有其他问题请邮件联系。